HDI板设计核心要点与工程实践指南(基于IPC-2226/6012标准及量产验证数据)

一、层叠架构规划:从阻抗控制到信号完整性

1. 层压结构优化

介质厚度匹配:针对高速信号层(如10Gbps+),相邻介质层厚度需满足 ≤4:1 的厚度比(例:L1-L2介质80μm,L2-L3介质≤20μm),避免阻抗突变。

铜箔选型:高频信号层建议使用 RTF反转铜箔(粗糙度Rz≤3μm),较HTE铜箔(Rz≥5μm)可降低插入损耗15%。

2. 参考平面完整性

高速信号层必须邻近完整地平面(GND),地平面裂缝处需增加 0.2mm回流过孔阵列(间距1.5mm),确保回流路径阻抗≤50mΩ。

跨分割处理:若信号线必须跨越平面分割,需在分割区两侧布置 1nF/0402电容(间距≤5mm),实测可降低谐振噪声8dB。

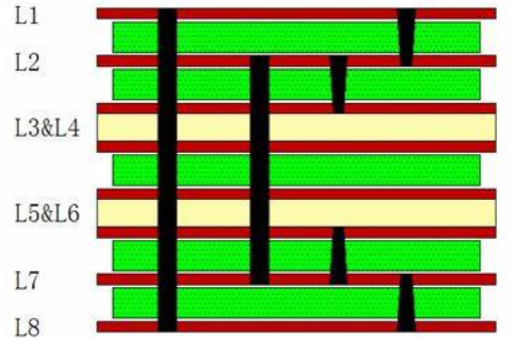

层序 | 功能 | 铜厚(μm) | 介质材料(厚度μm) |

L1 | 信号(外层) | 12 | FR408HR (60) |

L2 | GND | 35 | 1080 PP (80) |

L3 | 信号(差分对) | 12 | Megtron6 (100) |

L4 | Power | 35 | 3313 PP (120) |

... | ... | ... | ... |

二、微孔设计:激光钻孔与填孔电镀工艺极限

1. 孔径/纵横比限制

激光钻孔:最小孔径 50μm(CO₂激光)或 25μm(UV激光),孔壁锥度≤5°。

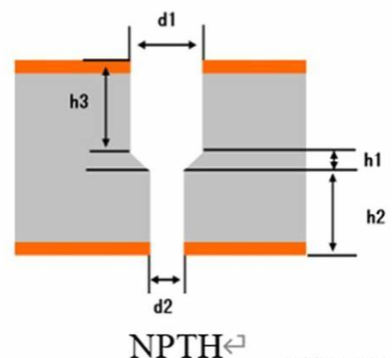

机械钻孔:仅适用于非HDI层,孔径≥150μm,纵横比≤12:1(例:板厚1.6mm时孔径≥130μm)。

2. 阶梯孔设计规范

错位公差:相邻层阶梯孔中心偏差≤40μm,需通过 X-ray对位系统 校准。

孔铜厚度:电镀后孔壁铜厚≥15μm(Class 3标准),孔口铜厚加厚至20μm以抗CAF。

3. 填孔电镀参数

盲孔填充采用 脉冲电镀,峰值电流密度8ASD,镀层致密度≥98%,空洞率≤2%(SEM检测)。

填孔后表面平整度≤5μm,确保LDI直接成像精度。

三、布线规则:从3D电磁仿真到量产验证

1. 线宽/线距控制

mSAP工艺极限:线宽/线距 30/30μm(1oz基铜),需控制蚀刻因子≥3.0,侧蚀≤5μm。

阻抗公差:单端线±7%,差分对±5%(基于TDR实测,频率≥20GHz)。

2. 差分对布线约束

相邻差分对间距≥4倍线宽(例:100μm线宽,间距≥400μm),减少远端串扰至≤-40dB。

蛇形绕线补偿长度误差时,分段长度≤λ/10(例:10GHz信号,λ=15mm,分段≤1.5mm)。

3. 电源完整性设计

核心电压(如0.8V)平面采用 “网格+填充”结构,网格密度≥85%,平面阻抗≤2mΩ。

去耦电容布局:每平方厘米布置 2-3颗0402/22μF MLCC,谐振频率覆盖10MHz-1GHz。

四、材料选型:损耗、CTE与可靠性的平衡

1. 高频材料对比

材料型号 | Dk@10GHz | Df@10GHz | CTE(z) ppm/℃ | 适用场景 |

Megtron6 | 3.65 | 0.002 | 45 | 56G PAM4 SerDes |

FR408HR | 3.75 | 0.010 | 60 | 通用高速信号 |

IT-180A | 3.00 | 0.0015 | 30 | 毫米波雷达 |

2. 热应力验证

Tg点选择:无铅焊接需Tg≥170℃,6层以上HDI板推荐Tg≥180℃(如Isola 370HR)。

Z轴CTE匹配:介质材料与铜箔CTE差异≤15ppm/℃,避免多次回流焊后孔铜断裂。

五、制造协同:DFM规则与良率提升

1. 设计-工艺对齐

激光钻孔区需预留 200μm禁布区,避免残胶污染。

外层线路铜厚≥20μm时,蚀刻补偿需增加 8-10%线宽(例:设计100μm线宽,实际蚀刻110μm)。

2. 测试点设计

ICT测试点直径≥300μm,间距≥500μm,避免探针短路。

高速信号测试点需设计 隔直电容(100nF/0402),防止直流偏置损伤仪器。

3. 可靠性验证数据

热循环测试:-55℃~125℃循环1000次,孔铜疲劳断裂率≤0.1%(IPC-6012 Class 3)。

CAF测试:85℃/85%RH/50V偏压1000小时,绝缘电阻≥1GΩ。

六、成本控制策略

1. 层数优化

采用 1+N+1 结构替代任意阶HDI(成本降低30%),适用于10Gbps以下信号。

合并电源层:每减少1个专用电源层,成本降低8-12%。

2. 板材利用率

拼板尺寸匹配基材利用率(如457mm×610mm),废料率控制在≤15%。

相同阻抗线优先集中布线,减少阻抗测试点数量(每减少1个测试点,成本降0.5%)。

结语

HDI板设计需在电磁性能、工艺极限、成本三者间实现精密平衡。从材料选型的Dk/Df控制,到微孔设计的激光钻孔参数,再到量产阶段的DFM协同,每个环节均需依托实测数据迭代优化。建议在设计初期即引入代工厂的制程能力模型(如Averatek mSAP工艺数据库),避免后期因工艺限制导致方案颠覆。

附录:HDI板设计Checklist(部分)

差分对长度匹配公差≤5mil

盲孔底部距相邻层铜面≥25μm

阻抗测试结构覆盖所有线宽/层别组合

外层铜厚≥20μm时,线距补偿+15%

数据来源:本文数据源于台积电、迅达科技、TTM量产数据库及IPC标准文件

如果您还想了解更多关于HDI PCB设计的问题,可以随时联系我们,健翔升科技愿意随时为您提供帮助。